4 тома 4] Технология производства полупроводников+Производство Чипа Полупроводниковое процесс Практическое учебное пособие Шестой издание+Дисциплинарная технология чипов+Упаковка SIP SIP и инженерное проектирование Полупроводниковые интегрированные схемы Производство

Вес товара: ~0.7 кг. Указан усредненный вес, который может отличаться от фактического. Не включен в цену, оплачивается при получении.

Описание товара

- Информация о товаре

- Фотографии

| 【Все 4 тома】 Технология производства полупроводников+производство чипов—— Учебное пособие по утилиту процесса процесса полупроводника (шестое издание)+Технология графических чипов+PIP SIP упаковка и проектирование инженерного проектирования | ||

| Ценообразование | 306.80 |

| Кодирование ISBN | 9787121260834 | |

| Полупроводниковые технологии производства | ||

| Ценообразование | 79.00 |

| Издатель | Электронная промышленная пресса | |

| Опубликованная дата | Июнь 2015 | |

| формат | 16 | |

| автор | (MEI) Кварк, (США) Тода, Хан Чжэншенг и другие переводы | |

| Количество страниц | 0 | |

| Кодирование ISBN | 9787121260834 | |

Введение

Эта книга подробно описывала историю развития полупроводников и поглотила различные новые технические материалы. Академические и промышленные круги имеют высокую оценку этой книги.Книга разделена на 20 глав. Согласно основной технической классификации производства полупроводников, расположены главы, включая базовую техническую информацию, связанную с производством полупроводников; объясните каждый крупный процесс; задний процесс перерастает интегрированную сборку цепей и упаковку.Кроме того, каждая глава предоставляет читателям проблему измерения качества и устранения сбоев, которые являются практическими проблемами, которые столкнутся с кремниевыми пластинами.

Оглавление

Глава 1 Введение в полупроводниковую промышленность

Цель

1.1 Введение

1.2 Развитие отрасли

1.3 Интеграция цепи

1.4 Интегрированное производство цепи

1,5 полупроводниковые тенденции

1.6 Электронный возраст

1.7 Занятие в производственной промышленности полупроводников

1.8 Резюме

Глава 2 Характеристики полупроводникового материала

Цель

2.1 Введение

2.2 Атомная структура

2.3 Цикл Таблица

2.4 Классификация материала

2.5 кремний

2.6 Дополнительный полупроводниковый материал

2.7 Резюме

Глава 3 Технология устройства

Цель

3.1 Введение

3.2 Тип схемы

3.3 Без структура компонентов

3.4 Структура компонентов источника

3.5 Эффект блокировки устройства CMOS

3.6 Продукты интегрированной цепи

3.7 Резюме

Глава 4 Приготовление кремния и кремния Sheae

Цель

4.1 Введение

4.2 Полупроводник -Крейд Силикон

4.3 Кристаллическая структура

4.4 Jingxiang

4.5 Рост монокристаллического кремния

4.6 Кристаллические дефекты в кремнии

4.7 Проверка кремния

4.8 Измерение качества

4.9 Внешняя задержка

4.10 Резюме

Глава 5 Химические вещества в производстве полупроводников

Цель

5.1 Введение

5.2 Материальная форма

5.3 Атрибуты материалов

5.4 Химикаты для мастерства

5.5 Резюме

Глава 6 управление динус в кремниевой пленке производство

Цель

6.1 Введение

6.2 Тип грязного

6.3 Источник и контроль грязных

6.4 Метод влажной очистки кремния.

6.5 Резюме

Глава 7 Измерение и дефектная проверка

Цель

7.1 Введение

7.2 Исследования измерения интегрированной схемы

7.3 Измерение качества

7.4 Аналитическое оборудование

7.5 Резюме

Глава 8 Контроль газа в полости ремесла

Цель

8.1 Введение

8.2 вакуум

8.3 вакуумный насос

8.4 Поток воздуха в полости ремесла

8,5 Остаточный анализатор газа

8.6 Плазма

8.7 Окрашивание ремесленного полости

8.8 Резюме

Глава 9 Обзор технологии интегрированного производства схем

Цель

9.1 Введение

9.2 Процесс процесса CMOS

9.3 Стадии производства CMOS

9.4 Резюме

Глава 10 Окисление

Цель

10.1 Введение

10.2 Оксидная пленка ...........................

20.3 Традиционная упаковка

20.4 Усовершенствованная сборка и упаковка

20.5 Измерение качества упаковки и сборки

20.6 Интегрированная инспекция упаковки схемы и исключение сбоев

20.7 Резюме

Приложение химическое вещество и безопасность

Приложение B Чистое управление управлением

Приложение C Блок

Приложение D как цвет функции толщины окисляющего слоя

Приложение E Light Equipment Hemicals для химии

ПРИЛОЖЕНИЕ F ГРАВИТЕЛЬНАЯ ХИМИЯ

| Графическая технология чипов | ||

| Ценообразование | 49.00 |

| Издатель | Химическая промышленность пресса | |

| Опубликованная дата | Июль 2019 | |

| формат | 32 | |

| автор | Тянь Минбо  | |

| Количество страниц | 300 | |

| Кодирование ISBN | 9787122339607 | |

Введение

В ответ на многоуровневые потребности входах, кандидатов и исследований и разработок#, под предпосылкой предоставления большого количества информации, «Diger Clear Technology» использует форму графики и текста, которая всесторонне и кратко вводит Принцип работы чипа, интегрированные схемы и производство. Процесс, новый прогресс, новые приложения и перспективы развития чипов.Под каждой главой“ ясно ясно&Rdquo; как обсудить путь, с правильной картинки, изображения и текста, и дайте его&Ldquo; фокус этого раздела”.Стремиться к простому и простому -для -понятном, простое -для -понятно; четкие уровни, четкие идеи; богатый контент, основные моменты; новый выбор материалов, подчеркивая приложения.

Эта книга может быть использована для студентов, таких как микроэлектроника, материалы, физика, точные инструменты, а также технические и технические сотрудники в смежных областях.

об авторе

Tian Minbo, Университет Цинхуа, Школа материалов, профессор, докторский супервайзер, в течение длительного времени занимается предварительным исследованием учебных материалов и достигал первоначальных достижений в области электронных материалов, упаковочных технологий, магнитных материалов и порошковые материалы.Темы, которые предполагались, являются: (1) крупные проекты научных фондов“ базовое исследование упаковки с высокой плотностью” (2) Международное проект сотрудничества&Ldquo; Zero Contraction Specing LTCC Research” (3)&Ldquo; пятнадцать&Rdquo; Pre -Research Project военной промышленности“ Новый тип уровня LCCC-3D MCM Technology Research” (4)“863&rdquo&Ldquo; исследования и разработка материалов серебристого раскладывания полимера” (5)“985” проект на лице&Ldquo; с низкой температурой Co -Burning Ceramic Multi -Layer Substrate и исследования упаковки с высокой плотностью и т. Д.

Оглавление

Глава 1  Введение в интегрированную схему

1.1  Обзор 2

1.1.1  от отдельных компонентов до интегрированной схемы 2

1.1.2  от кремниевого круглого чипа до чипа до упаковки 4

1.1.3  функция триода—— его можно сравнить с водными дорогами со шлюзой 6

1.1.4  N DITIC MOS (NMOS) Триод Принцип работы 8

1.1.5  Diend State Chateage Cuccepare на устройствах MOS 10

1.2  полупроводниковый кремниевый материал—— Core и Foundation интегрированной схемы 12

1.2.1  MOS -тип и транзистор биполярного узла 12

1.2.2  Диаграмма рисунка конструктора CMOS (тип типа P) 14

1.2.3&Nbsp; блок хранения флеш“ написать”“ стирание”“ читать&Rdquo; принцип работы 16

1.3  Классификация компонентов интегрированной цепи 18

1.3.1  функции и типы IC 18

1.3.2 ram и rom20

1.3.3  метод классификации полупроводниковых устройств 22

1.4  Процесс процесса процесса полупроводниковых устройств 24

1.4.1  передний процесс и задний корабль 24

1.4.2  IC -чип -процесс процесса введение 26

Забронировать на мысе чайный стол

Десять лучших вех в истории интегрированной схемы 28

Глава 2 от диоксида кремнезема до пластины

2.1  полупроводниковый кремниевый материал 36

2.1.1  кремний в настоящее время является важным полупроводниковым материалом 36

2.1.2  кристаллические дефекты в монокристаллическом кремнеоне 38

2.1.3  PN0 в примесях в PN Knot 40

2.1.4  Классификация сопротивления изоляторам, полупроводникам и проводникам по сопротивлению 42

2.2  от кремния к кремнию в кремнии до 99,99999999%высокого кремния 44

2.2.1  Процесс 44 от Spar сырья до полупроводниковых компонентов 44

2.2.2  от восстановления кремнезема до металлического кремния 46

2.2.3  выборы и рост Polysilicon 48

2.3  от полисиликона до монокристаллической кремниевой палочки 50

2.3.1  улучшить производство Polysilicon 50

2.3.2  Czochralski (метод CZ) Потяните мольсталлический кремний 52

2.3.3  районный районный роли

2.3.4  Причины и меры устранения в средней ошибке метода прямой тяги 56

2.4  от монокристаллического кремния до пластины 58

2.4.1  размер пластины продолжает расширять 58

2.4.2  обработка логотипа ориентации первые 60

2.4.3  разрезайте кремниевые пробелы на куски кремниевого круглого листа 62

2.4.4  кремниевый круг имеет множество различных типов 64

2.5  Polishing Film, Fire Retreat, Extension Film, Soi Film 66

2.5.1  Polishing Film and Anealing Film 66

2.5.2  Внешнее расширение 68

2.5.3  SOI Film 70

Забронировать на мысе чайный стол

&Ldquo; кремний - это сокровище, данное Богом”72

Глава 3  Процесс производства интегрированного производства цепи

3.1  интегрированная логика схемы LSI Структура 74

3.1.1  Структура двойного избирательного устройства 74

3.1.2  Кремниевая сетка MOS Структура 76

3.1.3  Кремниевая сетка CMOS Структура 78

3.1.4  Bicmos Device и SOI Device Structure 80

3.2&Процесс NBSP; LSI 82

3.2.1  Используйте оптические резьбы, чтобы сформировать экземпляр контактного отверстия и слоя проводки 82

3.2.2  воздействие, показывая 84

3.2.3  Оптическая гравюра проекта заменитель 86

3.2.4 “ отрицательный&rdquo“ положительный” Принцип восприятия клей с легким клей 88

3.2.5  процесс оптического резки 90

3.2.6   Очистка, окисление, окисление, изолирующая мембрана—— легкое кубинг 92

3.2.7 etquets изоляционной мембранной области—— Образование пленки окисления сетки 94

3.2.8  Сетчатый электрод многокристаллический рост кремния—— введите его в 96

3.2.9  огни и ионы бора в инъекции ваучера P—— OM Contact Погребен 98

3.2.10  металлическая мембрана рост на 1 -м слое—— электродные прокладки формация 100

3.2.11  бронзовая проводка Damascus Craft 102

3.2.12 как разработать нашу индустрия производства IC Chips 104

3.3  Классификация процессов и комбинация производства чипов IC 106

3.3.1  Основные ремесла в производстве чипов IC 106

3.3.2  IC CIP Mustance Compound Compress 108

3.3.3  модуляризация процесса 110

3.3.4  процесс субстрата и процесс проводки 112

Забронировать на мысе чайный стол

Ведущий мировой интегрированной индустрии 114

Глава 4  осаждение тонкого пленки и графическая обработка

4.1  компоненты DRAM и различные тонкие пленки 120, используемые в компонентах LSI

4.1.1  компонентная структура и различная тонкая пленка 120

4.1.2  изменение структуры конденсатора в DRAM 122

4.1.3  3D -структура DRAM

4.1.4  Применение тонких пленок в интегрированных цепях 126

4.2  Тонкое пленка и пленка для производства IC (1)—— PVD Метод 128

4.2.1&Производство NBSP; VLSI применяет различные типы пленки 128

4.2.2  применение поликристаллического кремниевого столба в интегрированной цепи 130

4.2.3&Металл 132 обычно используется в процессе NBSP;

4.2.4 вакуумное паровое покрытие 134

4.2.5  Иоонное распыление и распылительное покрытие 136

4.3  Тонкое пленка и пленка для производства IC (2)—— метод CVD 138

4.3.1&Метод CVD NBSP; для метода CVD, изготовленного VLSI 138

4.3.2  Основное реакционное устройство 140 в ССЗ

4.3.3  Plasma CVD (PCVD) Процесс передачи, реакции и образования пленки 142

4.3.4  различные комнаты для обработки в процессе пластин 144

4.4  Тонкое пленка и пленка для производства IC (3)—— сравнение различных методов 146

4.4.1  Сравнение различных методов формирования пленки 146

4.4.2  Метод образования термического оксида 148

4.4.3  образование термической оксидной пленки 150

4.4.4  тип и метод производства для VLSI 152

4.4.5  метод CVD для VLSI 154

4.5  улучшение и устранение проводки дефектов—— проводка CU замените Al -проводку 156

4.5.1 враги, которые влияют на срок службы электронных компонентов—— электрическая миграция 156

4.5.2  Образование формирования дефектов отключения и схемы, а также мер по профилактике и ремонту 158

4.5.3  CU проводка разум для Al -проводки 160

4.5.4  Используйте метод гальванизации, чтобы сделать проводку Cu 162

4.5.5  преимущества и недостатки алюминия для IC Chip 164

4.6  Источники света. Источники света продолжают прогрессировать до короткой длины волны 166

4.6.1 как обработать его в графику 166 от тонкой пленки 166

4.6.2  несколько часто используемых методов воздействия света 168

4.6.3  огни огней на окружающей технологии 170

4.6.4  изменение длины волны воздействия и соответствующей технической гарантии 172

4.6.5  Разработка и перспектива системы оптических резьб 174

4.7  Технология оптической экспозиции 176

4.7.1  Классификация и изменение устройства графического экспозиции 176

4.7.2  Метод экспозиции света 178

4.7.3  почти выставлен и узкий проекционный экспозиция 180

4.7.4  различные меры компенсации по положению в воздействии 182

4.8  Electronic Expusion и технология воздействия ионного пакета 184

4.8.1  Технология экспозиции электронного луча 184

4.8.2  технология недавней экспозиции (LEEPL) с низкимэлектронным лучей (LEEPL) 186

4.8.3  Технология экспозиции NBSP; Проекционная проекция по восстановлению x -Ray 188

4.8.4  Технология экспозиции NBSP;

4.9 сухое метод травления вместо влажного травления 192

4.9.1  применение технологии пленки в производстве VLSI 192

4.9.2  Сравнение сухого травления и влажного травления 194

4.9.3  Типы и травление сухого травления 196

4.9.4  Феномен реакции сухого травления (мода RIE) 198

4.9.5  Устройство травления плазмы с высокой плотностью 200

Забронировать на мысе чайный стол

Десять лучших предприятий мировой индустрии чипов 202

Глава 5  примеси легируют—— тепловая диффузия и инъекция ионов

5.1  процесс тепловой обработки в интегрированном производстве схемы 208

5.1.1&Горячий процесс (горячий процесс) 208 в NBSP; Процесс IC Chip Process

5.1.2  Технология формирования термической оксидной пленки 210

5.1.3  самый важный инспекционный фильм 212

5.2  процесс тепловой диффузии для примесей допинга 214

5.2.1  цель примесей в производстве производства LSI 214

5.2.2  Сравнение примесей, метод допированного ионов и метод тепловой диффузии 216

5.2.3  решает распределение концентрации тепловых диффузионных примесей 218

5.2.4  цель термообработки—— Продвижение, Пинг Фрэнк, Электрическая деятельность 220

5.2.5  Поведение примесей в кремнии 222

5.3  ТЕХНОЛОГИЯ ТЕХНОЛОГИЯ ДАПИНА—&Mdash; принцип инъекции ионов 224

5.3.1  Принцип инъекции ионной инъекции 224

5.3.2  Иоонное устройство впрыска 226

5.3.3  инъекция ионов с низкой энергией и отжиг высокой скорости 228

5.3.4  распределение концентрации ионной инъекции 230

5.4  ТЕХНОЛОГО ТЕХНОЛОГО ТЕХНОЛОГИЯ НАПРЯЖЕНИЯ (2)—— применение инъекции ионов 232

5.4.1  Стандартный сайт инъекции Triode MOS 232

5.4.2  Основная верхняя структура и градиент инвертора Структура 234

5.4.3  Одно верхняя формация 236

5.4.4  двойная формация 238

5.4.5  Применение инъекции ионов в CMOS 240

5.4.6  Иоонная инъекция для мелкого вязания 242

Забронировать на мысе чайный стол

“ Основная технология - это тяжелое оружие страны”244

Глава 6&Может ли nbsp; может ли закон Мура продолжать вступать в силу

6.1  Многослойная проводка вступила в четвертое поколение 246

6.1.1 много -личная проводка—— требования к адаптации к микросхемам и высокой интеграции 246

6.1.2  Multi -Layered Glayered Glayered и 2 -е поколение технология—— слой за слой и стеклянным потоком Ping248

6.1.3  технология многослойной проводки 3 -го поколения—— представьте CMP250

6.1.4  Многослойная технология проводки 4 -го поколения—— введение Damascus Craft 252

6.2  Медная проводка сингл Martin Gegunt

6.2.1  CU Damascus Plining постепенно заменяет al -проводку 254

6.2.2  Craftsmanship Damascus - это китайский Cloisonne Blue Metal Process 256

6.2.3  от Al Winding+W Plunger до Cu Double Damascus Wind 258

6.2.4  CU Двойная малазийская структура проводки и возможные проблемы 260

6.3&Может ли NBSP; может ли закон Мура продолжать вступать в силу?262

6.3.1  Две тенденции полупроводниковых устройств к огромной и микроэтажной разработке 262

6.3.2&Интеграция чипов NBSP; Продолжается продвигаться по законодательству Мура 264

6.3.3&Ldquo; закон Мура не является законом физики”,“ но описывает закон индустриализации”266

6.3.4 “ поднимите ноги, прыгайте вверх, чтобы выбрать яблоко”268

6.4  импорт новых материалов——&Ldquo; технология производства производства материалов”270

6.4.1  Многослойный слой проводки, пленка конденсации DRAM, проводка CU 270

6.4.2  Система кремниевого материала по -прежнему имеет потенциал (1) 272

6.4.3  Система кремниевого материала по -прежнему имеет потенциал (2) 274

6.4.4  Составное полупроводниковое полупроводниковое омоложение 276

6.5 как достичь высокой производительности устройства?278

6.5.1  требования к высокой производительности устройства для всей машины становятся выше и выше 278

6.5.2  Высокая производительность устройств зависит от новых ремесел и новых материалов 280

6.5.3  Начните с процесса субстрата и процесса проводки одновременно 282

6.6  от 100 нм до 7 нм—— поддерживает инновации материалов и технологий в качестве поддержки 284

6.6.1  Чистая кремниевая трубка MOS и Polysilicon/High-K-база Tube 284

6.6.2  Металлическая сетка/высокая K-bati Tube Tube и FIN Field Effect Transistor (FINFET) 286 286

6.6.3 90nm—&Mdash; Stock Silicon 288

6.6.4 45nm—— изоляционный слой с высоким K и металлические затворы 290

6.6.5 22nm—— FIN FEELCH EFFECT TRANSISTOR 292

6.6.6 7nm—— EUV Light Carvings и Sige-Channel294

Забронировать на мысе чайный стол

Сбор#集 集 集 集 集 集 集 集 296

Ссылка 297

Автор профиль 298

| Упаковка и инженерный дизайн чипсов | ||

| Ценообразование | 89.80 |

| Издатель | Tsinghua University Press | |

| Опубликованная дата | Декабрь 2019 года | |

| формат | 16 | |

| автор | Мао Чжунгу | |

| Количество страниц | 190 | |

| Кодирование ISBN | 9787302541202 | |

Введение

Сосредоточение внимания на инженерном дизайне - это характеристики этой книги#.

Различные типы инкапсуляции и ее характеристики используются, а затем объяснение внутренней структуры упаковки, а затем вводят знание упаковочного субстрата и полного производственного процесса;

После того, как читатель понимает основу этих знаний, полный процесс проектирования корпуса#在 在 在 在 在 在 и флип -чип, пакет,

Представить, как использовать автоматические инструменты проводки для облегчения электронных инженеров, чтобы быстро получить количество слоев и нечестивую информацию подложки на стадии оценки упаковки;

Основываясь на них, вводится сложный дизайн упаковки, такой как SIP, позволяющий читателям изучить полный процесс дизайна упаковки от мелководья до глубокого.Из -за страны

Большинство инженеров SI не поняли внутреннюю часть упаковки. Модель модели упаковки ограничена применением, когда моделирование SI ограничена применением. Следовательно, эта книга упакована

После завершения проекта также вводятся полные извлеченные электрические параметры упаковки WB. Извлеченная модель может быть непосредственно применена к модели IBIS.

#.

Эта книга очень подходит в качестве справочного материала для обучения дизайну упаковки.

об авторе

Мао Чжунгу окончил технологию микроэлектроники Университета электронных наук и технологий.

На протяжении более 20 лет глубоко выращивая индустрию электронных технологий, участвуя в высокоскоростной конструкции ПХБ, моделировании SI/PI, процессе моделирования PI и конструкции платформы PING моделирования, высокоскоростной конструкции упаковки IC и других работ. С богатым опытом.

Он работал в Shenzhen Huawei Technology Co., Ltd., Hisilicon Semiconductor Co., Ltd., Xingsen Express Circuit Technology Co., Ltd. и т. Д.EDA365 Форум специально приглашенный модератор.

Основная публикация

?

? »Huawei R & D 14 лет: те, кто вместе боролся вместе»

? "Основа пакета IC и примеры проектирования инженерного проектирования"

Оглавление

Глава 1 Упаковка для чипов 1

1.1 Обзор инкапсуляции чипов 1

1.1.1 Тенденция разработки упаковки чипов. 1

1.1.2 Технология подключения чипов. 3

1.1.3 WB Technology 3

1.1.4 Технология FC. 5

1.2 Пакет Leadframe 6

1.2.1 для упаковки. 6

1.2.2 DIP . 7

1.2.3 SOP 7

1.2.4 SOJ 8

1.2.5 PLCC Package 8

1.2.6 QFP 9

1.2.7 Пакет QFN 10

1.3 BGA Package. 11

1.3.1 PGA Package 11

1.3.2 LGA Package 12

1.3.3 TBGA Package. 12

1.3.4 PBGA Package 13

1.3.5 пакет CSP/ FBGA 14

1.3.6 WLCSP 15

1.3.7 Пакет FC-PBGA. 17

1.4 Комплексная упаковка структуры 18

1.4.1 MCM Пакет 19

1.4.2 SIP . 20

1.4.3 SOC Package 21

1.4.4 PIP . 22

1.4.5 POP 23

1.4.6 3D пакет. 25

1.5 Сводка этой главы 25

ГЛАВА 2 SUPSTRATE. 26. 26

2.1 Пакет подложка 26

2.1.1 Материал субстрата. 26

2.1.2 Процесс обработки субстрата. 28

2.1.3 Поверхность субстрата. 30

2.1.4 Алтарическое покрытие. 30

2.1.5 Линия алтаря. 30

2.1.6 Правила проектирования субстрата. 30

2.1.7 Образец образца образца образца образца. 31

2.2 Процесс обработки субстрата 31

2.2.1 Слоистая структура. 31

2.2.2 Подробный процесс обработки субстрата. 32

Глава 3 Введение в использование APD 52

3.1 Start Apd. 52

3.2 Рабочий интерфейс APD. 53

3.3 Установите параметры привычки 54

3.4 Установить ярлыки функции Функции 55

3.4.1 Функциональный ключ по умолчанию. 56

3.4.2 Просмотреть распределение комбинации функций. 56

3.4.3 Команды, соответствующие клавишу комбинации функций. 57

3.5 масштабирование 58

3.6 Установите опцию чертежа 59

......................................

7.2.7 Одиночный нарушение строки. 181

7.2.8 Дифференциальное и одностороннее перекрытие. 183

7.2.9. Автоматическое генерирование отчета об моделировании. 184

7.2.10 Save. 184

Глава 8 Дизайн упаковки высокоэффективной вспомогательный инструмент. 185

8.1 BGA Tube Foot Automatic Tool. 185

8.1.1 Введение программы и функции. 185

8.1.2 Программная операция. 186

8.1.3 Меры предосторожности для использования. 188

8.2 Смешанное сравнение сетки 189

8.2.1 Введение функции программы. 189

8.2.2 Программная операция. 190

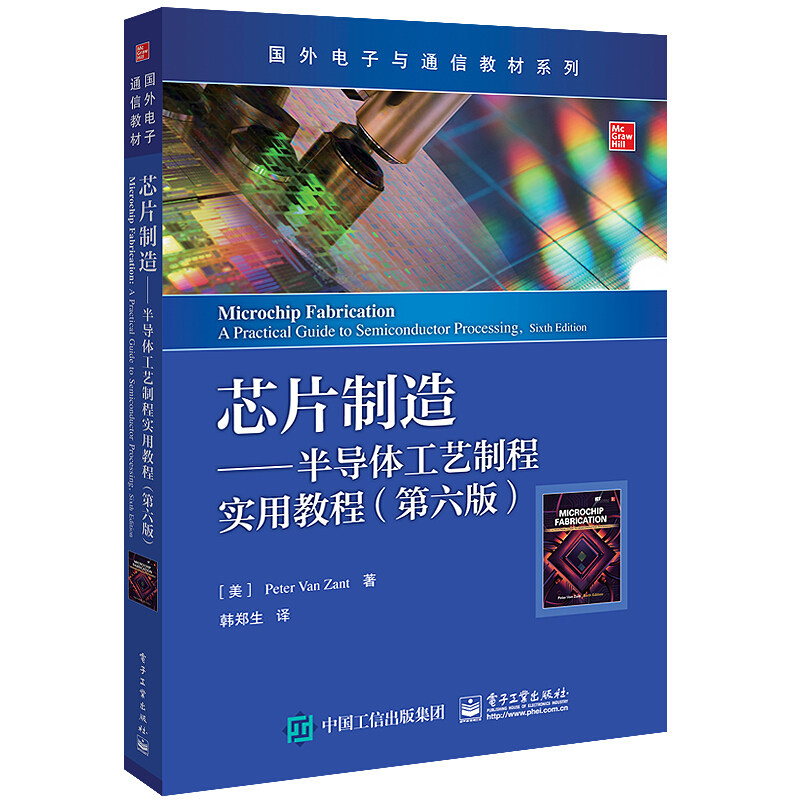

| Производство чипов—— Практическое учебное пособие по процессу процесса полупроводника (6 -е издание) | ||

| Ценообразование | 89.00 |

| Издатель | Электронная промышленная пресса | |

| Опубликованная дата | Декабрь 2020 года | |

| формат | 16 | |

| автор | (США) Питер Ван Зант | |

| Количество страниц | 384 | |

| Кодирование ISBN | 9787121399831 | |

Введение

Эта книга представляет собой профессиональную книгу, которая вводит полупроводниковые интегрированные цепи и технологию производства устройств и пользуется высокой репутацией в области полупроводника.Сфера обсуждения этой книги включает в себя каждую стадию полупроводниковых технологий: от подготовки сырья до упаковки, тестирования и транспортировки готовых продуктов, а также традиционных и современных технологий.Книга содержит подробные иллюстрации и экземпляры, дополненные резюме, упражнениями и богатыми терминами.Шестое издание пересмотрело новый прогресс в области производства микро -хип, обсудил расширенный процесс и заостренную технологию# -END для графических, легированных и пленку, так что физика и процессы, скрытые в сложных современных полупроводниковых производственных материалах. и мастерство, физика, физика, физика, физика, физика, физика и мастерство. Основная информация о химии и электронике легче понять.Основная особенность этой книги - избежать сложных математических проблем, внедряющих технологический контент процесса, и добавлять новые достижения в полупроводниковую промышленность, что может позволить читателям понять тенденцию разработки технологий процесса.

об авторе

Питер Ван Зант имеет широкий опыт работы в области технологий, обучения, консалтинга и письма. Он работал в IBM и Texas Instruments (TI), а затем в Силиконовой долине. И монолитные воспоминания о производстве и руководящей должности.Он также служил преподавателем в Foothill College в Лос -Анджелесе, штат Калифорния, чтобы преподавать полупроводниковые курсы и высокие курсы# -уровня для первоначальных инженеров по ремеслу.Он - «Глоссарий технологий полупроводников (третье издание),« интегрированное текст цепей »,« безопасность »и« инкапсуляция чипов »,« Интегрированные тексте текста »и« Первое руководство по безопасности ». Руководство« Автор (Руководство по упаковке чипов) ПолемЕго книги и учебные пособия были приняты многими производителями чипов, промышленными поставщиками, колледжами и университетами.

Хан Чжэншенг, мужчина, исследователь/профессор научно -исследовательского института микроэлектроники Китайской академии наук, докторант. Процесс тестирования, директор Департамента продукта Силиконового инженерного центра и лицо, отвечающее за проект/проект.Национальные специальные разрешения.Национальный эксперт по проекту естественного фонда.

каталог