Вторая книга, основанная на встроенной системе FPGA, Altera Soc FPGA Ren Aifeng и другие отредактировали Xi'an University of Electronic Science and Technology Press 9787560634517

Вес товара: ~0.7 кг. Указан усредненный вес, который может отличаться от фактического. Не включен в цену, оплачивается при получении.

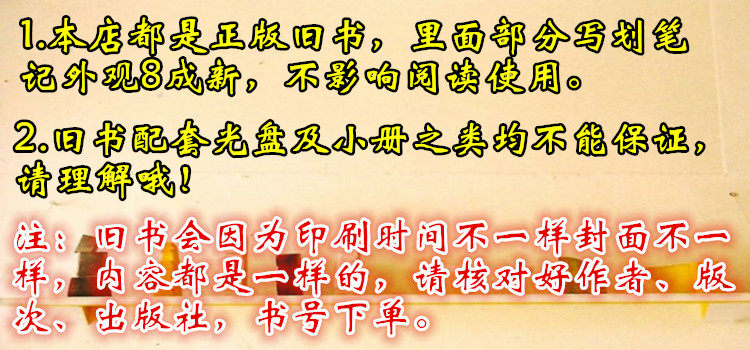

Описание товара

- Информация о товаре

- Фотографии

Оглавление

Главы, основанные на резюме дизайна встроенной системы SOCFPGA

1.1 Проблемы и возможности встроенного SOC Design

1.2 Решения, предоставленные Altera

1.2.1 Серия устройств

1.2.2 Дизайн программных инструментов и встроенных процессоров

1.2.3 IP -функция, которую можно использовать

1.2.4 SOCFPGA Development Kit

Глава 2 Профиль устройства серии Alterasocfpga

2.1 Введение в socfpga

2.2 Устройство циклонева

2.3 Устройство ARRIAV

Глава 3 Применение инструмента разработки Quartusieda

3.1 Введение в метод проектирования современной цифровой системы

3.1.1 Метод проектирования графического интерфейса пользователя

3.1.2 Процесс проектирования цифровой системы EDA

3.1.3 quartusii13.0eda.

3.2 Quartusil13.0

3.3 Процесс разработки программного обеспечения Quartusiieda

3,4 Ввод проектирования квартазила

3.4.1 Создайте новый проект

3.4.2 Установить файл редактирования схемы схема

3.4.3 Установить файлы редактирования текста

3.4.4 Установите файл редактирования памяти

3.4.5 Примеры проектирования

3.5 Компиляция проектных проектов

3.5.1 Проект комплексный

3.5.2 Настройки опции компилятора Quartusii

3.5.3 распределение выводов

3.5.4 Анализ результатов компиляции проекта

3.6 Проверка моделирования проектных проектов

3.6.1 Architecture Architecture SoftwareIm Software

3.6.2 SoftwareM

3.7 Анализ времени времени времени

3.7.1 Основные параметры анализа времени

3.7.2 Основные этапы анализа времени

3.7.3 Отчет об анализе просмотра времени

3.8 Программирование устройства

Глава 4 Инструмент разработки системы QSYS

4.1 Профиль QSYS

4.1.1 Введение технологии SOPC

4.1.2 QSYS и SOPC Development

4.1.3 Функциональные характеристики QSYS

4.1.4 QSYS Преимущества

4.2 Процесс проектирования QSYS

4.3 пользовательский интерфейс QSYS

4.3.1 Страница системного компонента

4.3.2 Страница поддержки системы

4.3.3 Страница опции системы

4.3.4 Команда меню QSYS

4.4 пользовательские пользовательские компоненты QSYS

4.4.1 Композиция компонента QSYS

4.4.2 Редактор компонентов QSYS

4.4.3 Индивидуальный компонент экземпляра 1DDS Сгенерирует модуль сигнала

4.4.4 Custom Component Encement 2 Ethernet Controller W5300 Control

Глава 5 Niosiieeds встроенный процессор дизайн процессора

Глава 6 HPS дизайн модели на основе QSYS

Глава 7 Встроенная система системы на основе SOCEDS

Глава 8 Дизайн DSP на основе Armsocfpga

Глава 9 OpenCl Введение и применение