- Таобао

- Техника

- Электроника

- Прочие электронные компоненты

- Двигатели СК

- 564672587002

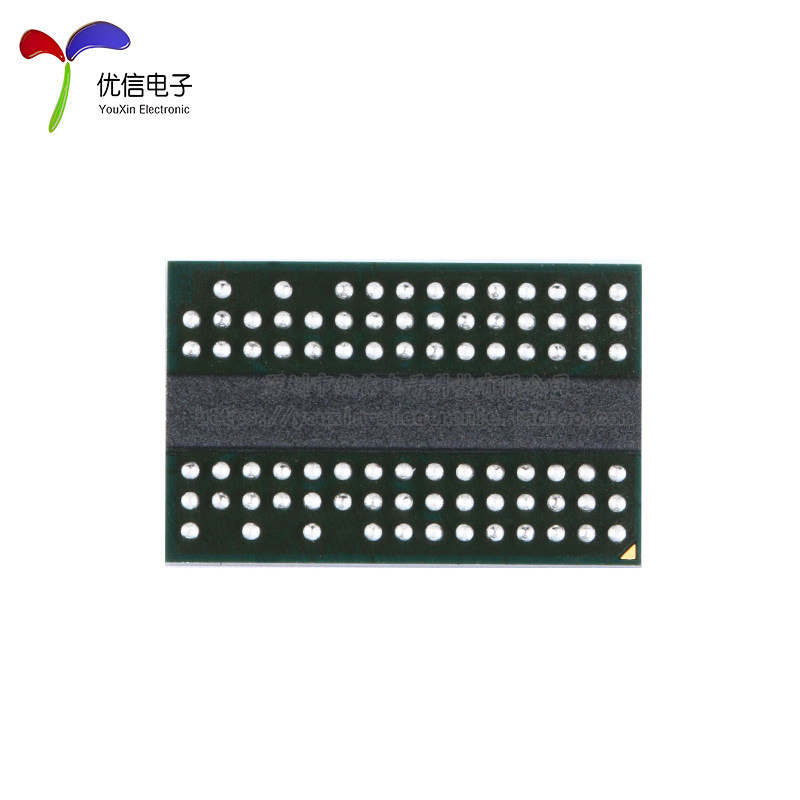

Оригинальный подлинный патч W9751G6KB-25 WBGA-84 512MBIT

Вес товара: ~0.7 кг. Указан усредненный вес, который может отличаться от фактического. Не включен в цену, оплачивается при получении.

Описание товара

- Информация о товаре

- Фотографии

ОригиналВкус

1 тарелка/209 шт.

Ссылка на документ PDF:

http://www.winbond.com.tw/hq/product/specialty-dram/ddr2-sdram/?__locale=zh&partNo=W9751G6KB

Функции

Питание: VDD, VDDQ = 1,8 В ± 0,1 В

Архитектура с двойной скоростью передачи данных: две передачи данных за такт.

CAS Latency: 3, 4, 5, 6 and 7

Burst Length: 4 and 8

Двунаправленные дифференциальные стробы данных (DQS и /DQS) передаются/принимаются вместе с данными.

Выровнено по краю для данных чтения и по центру для данных записи

DLL выравнивает переходы DQ и DQS с тактовой частотой.

Дифференциальные тактовые входы (CLK и /CLK)

Data masks (DM) for write data

Команды, вводимые на каждом положительном фронте CLK, данные и маска данных относятся к обоим фронтам /DQS.

Добавлена программируемая аддитивная задержка /CAS для повышения эффективности команд и шины данных.

Задержка чтения = аддитивная задержка плюс задержка CAS (RL = AL + CL)

Регулировка импеданса внекристального драйвера (OCD) и оконечная нагрузка на кристалле (ODT) для лучшего качества сигнала

Операция автоматической предварительной зарядки для пакетного чтения и записи

Auto Refresh and Self Refresh modes

Предварительное понижение мощности и активное понижение мощности

Write Data Mask

Задержка записи = Задержка чтения — 1 (WL = RL — 1)

Interface: SSTL_18